- This event has passed.

原位去嵌入 (ISD) 線上研討會

04/29/2021 @ 11:00 am - 12:00 pm

如果測試夾具和校準物件具有不同的阻抗,則傳統的去嵌入方法會在被測物(DUT)結果中產生違反因果性的誤差。本演講將介紹通過軟體而非硬體來解決這種阻抗差異的原位去嵌入(In-Situ De-embedding 或 ISD),因而能提高去嵌入精度,也同時降低硬體成本。現在IEEE 370 標準將ISD的開創性技術稱為“阻抗校正方法”。以下主題將使用50+ GHz的實際測量範例來進行討論:

- 什麼是因果性關係?

- 什麼是原位去嵌入(ISD)。

- 將ISD結果與仿真,其他去嵌入工具和Delta L方法進行比較。

- 違反因果性去嵌入如何影響連接器的規格測試。

- 如何自動消除不同傳播遲延以獲得更可預測的去嵌入結果。

- 如何從1x開路和1x短路推導等效的2x直通。

- 如何提取沒有 spikes 和 glitches 的準確的PCB走線衰減。

- 如何經由與去嵌入後的PCB走線吻合所有IL,RL,NEXT,FEXT和TDR / TDT來提取PCB的材料屬性(DK,DF,粗糙度)。

- PCIe 5.0 規格: 什麼是 ccICN ?

演講者:

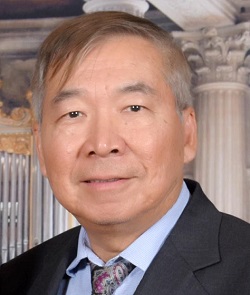

AtaiTec 公司創辦人兼總裁黃清照博士擁有30多年的高速設計與信號完整性(Signal Integrity 或 SI) 軟體開發經驗。曾擔任IBM的顧問工程師,TMA的研發經理,Rambus的SI經理以及Optimal的資深副總裁。黃總裁是IEEE的資深會員,發明原位去嵌入(ISD)。他畢業自台灣大學電機系,並於美國俄亥俄州立大學 (Ohio State University) 獲得電機碩士與博士學位。

Traditional de-embedding methods can give non-causal error in device-under-test (DUT) results if the test fixture and calibration structure have different impedance. This presentation introduces In-Situ De-embedding (ISD) that addresses such impedance difference through software instead of hardware, thereby improving de-embedding accuracy while reducing hardware cost. IEEE 370 standard now refers to ISD’s pioneering technique as “impedance corrected method”. The following topics will be discussed with up to 50+ GHz measurement examples:

- What is causality?

- What is In-Situ De-embedding (ISD).

- Comparison of ISD results with simulation, other de-embedding tools and Delta L method.

- How non-causal de-embedding affects connector’s compliance testing.

- How to automatically de-skew for more predictable de-embedding results.

- How to derive effective 2x thru from 1x open and 1x short.

- How to extract accurate PCB trace attenuation that is free of spikes and glitches.

- How to extract PCB’s material property (DK, DF, roughness) by matching all IL, RL, NEXT, FEXT and TDR/TDT of de-embedded PCB traces.

- PCIe 5.0 spec and ccICN, etc.

Speaker:

Dr. Ching-Chao Huang, AtaiTec founder and president, has more than 30 years of high-speed design and SI software development experience. He was advisory engineer at IBM, R&D manager at TMA, SI manager at Rambus and Sr. VP at Optimal. Dr. Huang is an IEEE senior member and and he pioneered In-Situ De-embedding (ISD) for causal and accurate de-embedding. He received his BSEE from National Taiwan University and MSEE and PhD from Ohio State University.

https://ataitec.com/docs/In-Situ_De-embedding.pdf

https://ataitec.com/docs/ISD_advantages.pdf

https://www.facebook.com/ataitec

https://www.linkedin.com/company/ataitec